Анализ цепей питания печатной платы в программе PowerDC пакета Allegro Sigrity Cadence

Анализ цепей питания печатной платы в программе PowerDC пакета Allegro Sigrity Cadence

Оглавление

1. Введение

2. Конвертация файла печатной платы для программы PowerDC.

3. Зарисовка упрощенной схемы питания печатной платы.

4. Импорт печатной платы в проект PowerDC и настройка её характеристик.

5. Ввод данных в проект о цепях, источниках напряжения, потребителях, межсоединениях и их параметрах.

7. Замечания по работе с программой.

8. Заключение

1. Введение

Я работаю инженером, участвую в разработке радиоэлектронной аппаратуры. Недавно пришлось столкнуться со следующей задачей. Для проектируемого устройства была выбрана современная элементная база и разведена печатная плата, которую передали на завод для изготовления. Были проведены предварительные расчеты токов при работе устройства, которые оказались достаточно большими по некоторым цепям (например, 8А по цепи 1,1В, 6,5А по цепи 1,8В и т.д.). Толщина проводящих слоев печатной платы небольшая, у некоторых слоев 0,018мм, а допуски на просадку напряжений для микросхем-потребителей около 5%, поэтому возникла необходимость уточнить величины падения напряжений. После того, как на заводе-изготовителе подогнали разведенную плату под свои технические нормы, они прислали печать на проверку. Необходимо было провести дополнительный анализ разводки печатной платы на падение напряжений и плотность токов на печатных проводниках для выявления узких мест. К сожалению, из-за плотности разводки и невозможности по разным причинам увеличить количество слоев платы, не удалось подключить входы обратной связи источников питания к самому близкому к потребителю месту, поэтому влияние подстройки напряжения источников питания не такое большое, как хотелось, и при расчете его решили не учитывать.

После составления эквивалентных схем печати платы и расчетов вручную, а затем с помощью моделей в программе LTSpice, был найден гораздо более быстрый, удобный и функциональный инструмент – программа PowerDC из пакета Allegro Sigrity Cadence. В программе PowerDC можно быстро промоделировать разведенную печатную плату по постоянному току и выявить участки с наибольшим падением напряжения, наибольшей плотностью тока и рассеиваемой мощностью, посмотреть величину тока через переходные отверстия, а также откорректировать печать и промоделировать печатную плату заново. В пакет Allegro Sigrity Cadence входят и другие программы, с помощью которых можно проводить тепловые расчеты печатной платы, расчеты по переменному току, расчет резонансных участков и импеданса проводников и так далее, но в данной статье я расскажу только о программе PowerDC, анализ в которой уже является большой подмогой инженеру.

Весь процесс анализа можно разбить на несколько этапов:

1. Конвертация файла печатной платы из формата Altium Designer в формат, пригодный для PowerDC.

2. Зарисовка упрощенной схемы питания печатной платы на основе принципиальной электрической схемы и разводки платы.

3. Импорт печатной платы в проект PowerDC и настройка её характеристик – материалов, толщин слоев, характеристик контактных площадок и т.д.

4. Ввод данных в проект о цепях, источниках напряжения, потребителях, межсоединениях и их параметрах.

5. Анализ результатов моделирования, выработка рекомендаций по коррекции разводки. Корректировка и повторный анализ при необходимости.

Повторение пункта 5 до тех пор, пока результаты моделирования не будут удовлетворительными.

По порядку рассмотрим каждый пункт.

2. Конвертация файла печатной платы для программы PowerDC.

На входе мы имеем файл печатной платы *.PcbDoc программы Altium Designer. Сначала надо перевести файл печати в читаемый программой PowerDC. Для этого делаем следующие шаги.

1. В Altium Designer (скриншоты сделаны для версии 15) необходимо открыть плату и создать ODB++ файлы. Для этого выбираем: File→ Fabrication Outputs→ODB++ Files. Я сохранял с теми настройками, которые выставлены по умолчанию (рис. 2.1).

Рис. 2.1. Окно OBD++ Setup программы Altium Designer

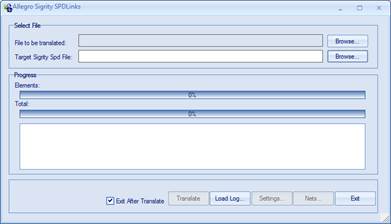

2. Запускаем Cadence Allegro Sigrity Suite Manager, выбираем в списке CAD Translators→SPDLinks→CAD Translators. Указываем файл *.zip для конвертации разводки платы (архив ODB++ Files файлов, который был создан Altium Designer) и путь сохранения *.spd файла (рис. 2.2). Можно установить настройки конвертации, вызывав окно Cadence OdbExtractor нажатием на клавишу Settings…. Я оставил все настройки по умолчанию.

Рис. 2.2. Окно Allegro Sigrity SPDLinks

3. Нажимаем на кнопку Translate и наблюдаем процесс конвертации. После конвертации получаем *.spd файл слоев платы, который будем далее использовать в программе PowerDC.

3. Зарисовка упрощенной схемы питания печатной платы.

Упрощенная схема питания включает в себя анализируемые цепи питания с указанием микросхем-источников, микросхем-потребителей, межсоединений (проходных резисторов, катушек и т.д.), напряжений и токов цепей.

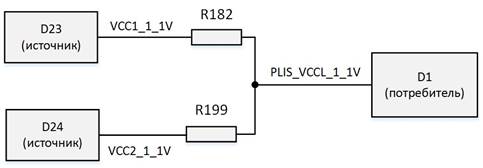

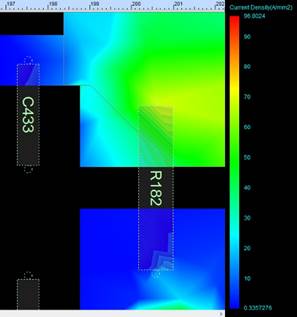

В моей схеме было около десятка цепей, которые необходимо было проанализировать. Все они были схематически нарисованы таким образом, как показано на рисунке 3.1. Я решил сначала рассмотреть одну из самых проблемных. Выглядит она следующим образом: есть два источника напряжения (VRM) D23 и D24, которые работают на одного потребителя (Sink) D1, а связь между ними обеспечивается через два проходных резистора (Interconnects) R182 и R199 (номиналом 0,001 Ом, используются для замеров тока и напряжения в процессе настройки устройства). У источников питания есть входы Vsense, служащие для подстройки выходного напряжения, их рассмотрим позже на примере другой микросхемы (D35). На примере этой цепи можно рассмотреть практически все этапы ввода схемы для анализа в программу PowerDC.

Рис. 3.1. Схематическое изображение анализируемой цепи питания печатной платы

4. Импорт печатной платы в проект PowerDC и настройка её характеристик.

1. Запускаем в Allegro Sigrity Suite Manager программу PowerDC.

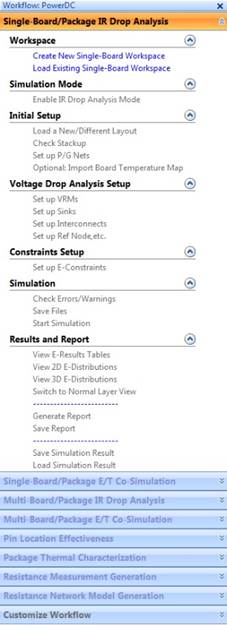

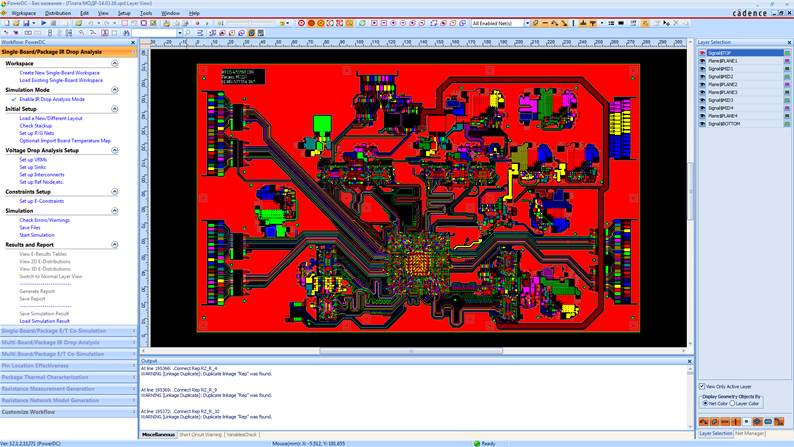

2. Слева в меню выбираем группу Single-Board/Package IR Drop Analysis (рис. 4.1).

Рис. 4.1. Окно Workflow: PowerDC и меню Single-Board/Package IR Drop Analysis.

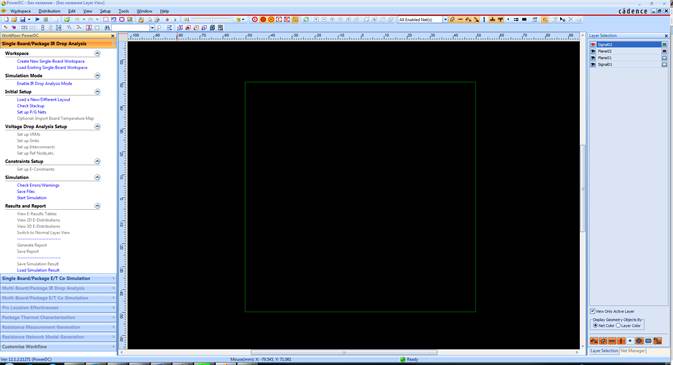

3. В меню Single-Board/Package IR Drop Analysis щелкаем на Create New Single-Board Workspace – создаём новую рабочую область, после чего становятся доступны следующие пункты меню (рис. 4.2). Двигаясь вниз по пунктам и выполняя каждый, в конце концов мы увидим результаты анализа платы и посмотрим отчет.

Рис. 4.2. Рабочая область программы PowerDC

4. Ставим галочку на пункте меню Enable IR Drop Analysis Mode – указываем, что хотим провести этот тип анализа – анализ по постоянному напряжению цепей питания.

5. Нажимаем на Load a New/Different Layout и выбираем либо Create a new layout (создать новый слой), либо Load an existing layout (загрузить внешний слой). Мы загружаем слои из внешнего файла, используя созданный в п.2.3 *.spd файл (рис. 4.3).

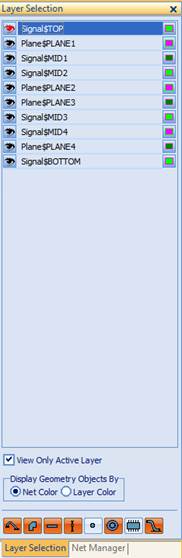

После загрузки слоев рисунок платы появится в центральной рабочей области. Интерфейс программы интуитивно понятен. Сверху расположены различные панели инструментов (о них позже). Слева находится меню основных шагов рабочего процесса при анализе платы. Справа две вкладки – Layer Selection и Net Manager, после проведения симуляции при переключении в режим View 2D E—Distributions появится ещё третья вкладка Distribution. В верхней части вкладки Layer Selection мы можем выбрать отображаемые слои (рис. 4.4). В нижней части вкладки Layer Selection выбираются элементы, которые необходимо отображать на слое: дорожки (Trace), отверстия (Via), контактные площадки (Pad), шины (Node) и т.д. На вкладке Net Manager можно выбрать цепи, с которыми мы работаем, и настроить их тип. Кроме этого, снизу и слева могут появляться дополнительные окна при выполнении каких-либо операций. Двигаемся дальше.

Рис. 4.3. Рабочая область программы PowerDC после загрузки слоев платы

Рис. 4.4. Вкладка Layer Selection со списком слоев платы.

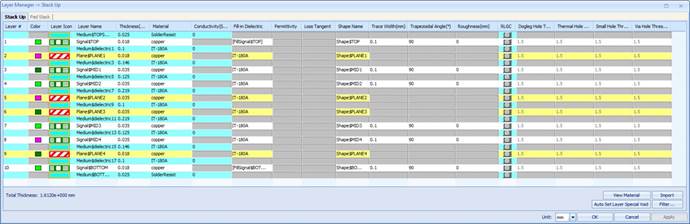

6. В меню Single—Board/Package IR Drop Analysis нажимаем на пункт Check Stackup, после чего появляется окно Layer Manager и вкладка Stack Up (рис. 4.5).

Рис. 4.5. Окно Layer Manager→ Stack Up

7. На вкладке Stack Up проверяем состав слоев платы и их характеристики, редактируем параметры материалов (проводящих и диэлектрических слоев). Если применяемого материала нет в списке, тогда можно создать новый материал и ввести его параметры. На вкладке Pad Stack можно редактировать параметры контактных площадок.

У меня почему-то толщина слоев устанавливается не точно по размерам из Altium Designer, а больше или меньше на тысячные доли. Из-за чего этот глюк – не разобрался, просто выставил точные значения.

5. Ввод данных в проект о цепях, источниках напряжения, потребителях, межсоединениях и их параметрах.

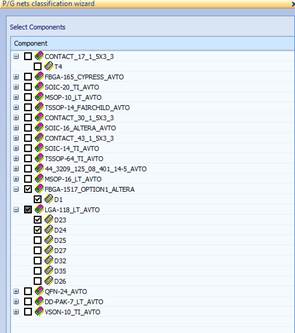

1. Нажимаем в меню Single-Board/Package IR Drop Analysis на пункте Set up P/G Nets→Setup P/G nets для того, чтобы настроить цепи питания и земли для нужных микросхем (D23 и D24 в моем случае). В окне Select Component выбираем микросхемы для анализа (рис. 5.1), у которых хотим установить типы цепей (питания, земли или сигнальные) щелкаем на кнопку Далее >.

Рис. 5.1. Окно Select Component меню Set up P/G Nets→Setup P/G nets

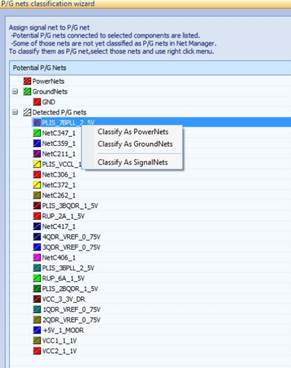

2. Устанавливаем типы цепей – для этого нужно щелкнуть правой кнопкой на цепи и выбрать Classify→As PowerNets, или As GroundNets, или As SignalNets (рис. 5.2).

Рис. 5.2. Окно Assign signal net to P/G net меню Set up P/G Nets→Setup P/G nets

3. В следующем окне можем установить номинальное напряжение цепи питания, а можно оставить поле пустым и щёлкнуть Готово, как и сделаем (рис. 5.3).

Рис. 5.3. Окно Assign power net voltage and P/G net paring меню Set up P/G Nets→Setup P/G nets

4. После этого на вкладке справа Net Manager (окно Net List (Sort diff nets first)) необходимо выбрать цепи для анализа. Если этого окна не видно, то для того чтобы его открыть, надо щелкнуть на пункте меню слева Set up P/G Nets и выбрать Skip setup P/G Nets. Отмечаем нужные для анализа цепи в окне Net List (Sort diff nets first) галочками. У меня это цепи VCC1_1_1V, VCC2_1_1V, PLIS_VCCL_1_1V и цепь земли GND. В этом окне необходимо выбрать все цепи в схеме, которые присутствуют в данной цепи питания, начиная от потребителя и заканчивая источником, вместе с цепями земли (относительно них обычно указывается напряжение источника). Все анализируемые цепи необходимо отметить галочками и установить их вид. Они нужны будут в том числе и для того, чтобы указывать элементы межсоединений.

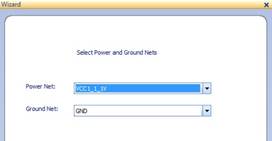

5. Устанавливаем источники напряжения (VRMs). Для этого щелкаем на пункте меню Set up VRMs. Источники напряжения можно настроить в ручном режиме (Create manually) или используя схему и определяя их из файла слоёв (Create by using existing circuits defined in the layout file). Воспользуемся вторым вариантом. Сначала указываем цепь питания от источника D23 до резистора R182 (Цепь VCC1_1_1V). Для этого необходимо указать сначала цепь питания, источником которой является источник питания и соответствующую ему цепь земли (рис. 5.4). В списке цепей будут только те цепи, которые указаны для анализа галочками в окне Net List (Sort diff nets first)!

Рис. 5.4. Меню Select Power and Ground Nets окна Wizard настройки источника питания

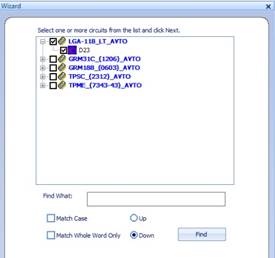

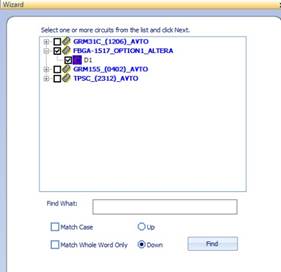

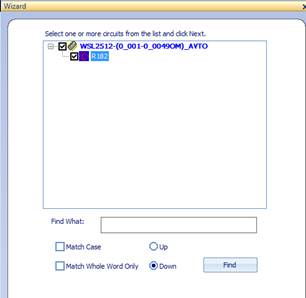

Щелкаем Далее >, после чего появится список элементов, связанных с этой цепью, отсортированный по типам корпусов. Выбираем нужный нам источник напряжения D23 (рис. 5.5) и щелкаем Далее >.

Рис. 5.5. Меню Select one or more circuits from the list and click Next окна Wizard настройки источника питания

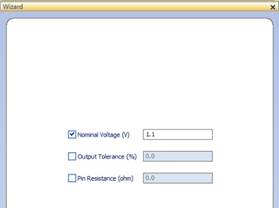

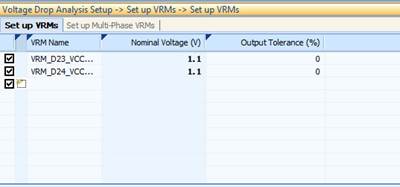

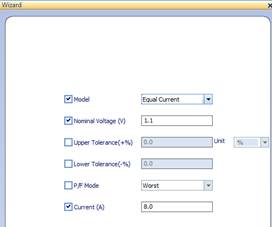

Устанавливаем номинальное напряжение, можно также указать погрешность установки и сопротивление выводов (рис. 5.6). Щелкаем Далее >, проверяем данные и щелкаем на Готово. Внизу страницы появится окно Set up VRMs с таблицей источников питания (рис. 5.7).

Щелкаем правой кнопкой на пункте Set up VRMs меню Single—Board/Package IR Drop Analysis и выбираем VRM Wizard и аналогично добавляем источник D24.

Рис. 5.6. Меню установки напряжений окна Wizard настройки источника питания

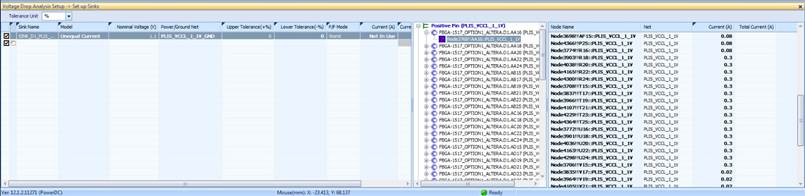

Рис. 5.7. Вкладка Set up VRMs окна Voltage Drop Analysis Setup

6. Задаем потребителей (Sinks), щелкнув на пункте Set up Sinks. Аналогично можно работать либо в ручном режиме, либо используя цепи схемы. Мы выбираем второй вариант и нажимаем Далее >. Затем выбираем цепь, которая поступает непосредственно на вход потребителя (PLIS_VCCL_1_1V) и цепь земли (GND), нажимаем Далее >. Выбираем элемент-потребитель, у меня это микросхема D1 (рис.5.8) и нажимаем Далее >.

Рис. 5.8. Меню Select one or more circuits from the list and click Next окна Wizard настройки потребителя

В появившемся окне необходимо настроить параметры потребителя. Существует три модели для расчета:

· Equal Current (равный ток) – в такой модели все токи, которые протекают через входные ножки потребителя, равны. При этом напряжение на контактах отличается.

· Equal Voltage (равное напряжение) – в этой модели при расчете считается, что на всех ножках одинаковое напряжение, как будто они объединены. При этом указывается напряжение между положительным и отрицательным контактом потребителя. Во время расчета за счет разных токов на контакты потребителя программа пытается сделать одинаковые напряжения.

· Unequal Current (неравный ток) – в этой модели токи, протекающие через контакты микросхемы, могут быть разными. Пользователь может их указать вручную или ввести с помощью «токовой карты». Вручную можно установить ток для выбранной микросхемы для каждой ножки в окне Voltage Drop Analysis Setup→Set up Sinks внизу в правой колонке (рис. 5.9). Во втором случае для расчета можно загрузить «токовую карту» – «Current mapping file» и указать вручную, в какие группы объединены ножки питания и земли, и какие токи протекают в группах контактов микросхемы.

Рис. 5.9. Меню установки токов на ножках микросхемы в окне Voltage Drop Analysis Setup→Set up Sinks

Я для расчета выбрал модель расчета по одинаковому току Equal Current. Необязательные параметры для расчета – номинальное напряжение потребителя и допустимые погрешности установки напряжения. Обязательно указываем потребляемый ток (рис. 5.10), нажимаем Далее >.

Рис. 5.10. Меню установки параметров потребителя окна Wizard

Если было выбрано несколько микросхем, то указываемый ток устанавливается для каждой микросхемы. Проверяем параметры и нажимаем Готово.

Для добавления нового потребителя необходимо щелкнуть правой кнопкой на Set up Sinks (или внизу на поле таблицы Voltage Drop Analysis Setup→Set up Sinks) и выбрать Sink Wizard.

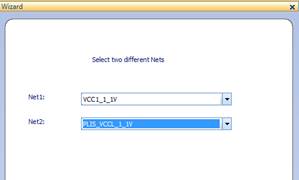

7. Нажимаем на пункте Set up Interconnects меню Single-Board/Package IR Drop Analysis и задаем межсоединения (Interconnects), в нашем случае это R182 и R199. Аналогично можно работать либо в ручном режиме, либо используя цепи схемы. Выбираем второй вариант, нажимаем Далее >. Выбираем две цепи, между которыми находится элемент. Для R182 это будет VCC1_1_1 и PLIS_VCCL_1_1V (рис. 5.11), нажимаем Далее>.

Рис. 5.11. Меню Select two different Nets окна Wizard установки параметров потребителя

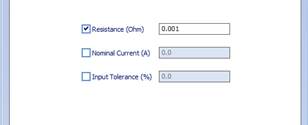

Выбираем необходимый резистор, жмем Далее > (рис. 5.12). Устанавливаем сопротивление резистора. Дополнительно можно установить номинальный ток и отклонение, нажимаем Далее > (рис. 5.13). Проверяем данные и нажимаем Готово.

Рис. 5.12. Меню Select one or more circuits from the list and click Next окна Wizard установки параметров потребителя

Рис. 5.13. Меню установки параметров потребителя окна Wizard

Нажимаем правой кнопкой на Set up Interconnects, выбираем Add и повторяем процедуру для R199, выбирая соответствующие цепи (VCC2_1_1V и PLIS_VCCL_1_1V).

8. После того, как добавлены необходимые источники напряжения, потребители, межсоединения, можно изменить введенные данные или добавить новые. Чтобы добавить новые элементы, надо выбрать нужный пункт (Set up VRMs, Set up Sinks, Set up Interconnects) в меню Single—Board/Package IR Drop Analysis и затем в таблице снизу щелкнуть правой кнопкой на свободном месте (также можно щелкнуть правой кнопкой на нужном пункте меню Single-Board/Package IR Drop Analysis) и выбрать VRM Wizard, SINK Wizard и т.д.

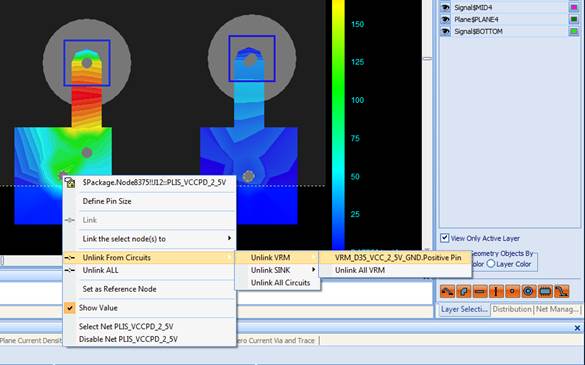

9. В пункте Set up Ref Node, etc. меню Single—Board/Package IR Drop Analysis можно настроить параметры, необходимые для расчета потерь мощности, а именно: цепь опорного напряжения и разрешение сетки изображения платы. Надо иметь ввиду, что при установке слишком большого разрешения (примерно больше 1000*1000 элементов), расчет может занять очень много времени!

10. В пункте Set up E-constraints меню Single—Board/Package IR Drop Analysis можно установить ограничения для элементов (по плотности тока, тока и плотности тока через переходные отверстия и т.д.).

11. Сейчас я ввел одну цепь питания (1,1 В) для расчета, которая состоит из двух источников напряжения, одного потребителя, двух проходных резисторов. Для моделирования необходимо, чтобы у меня были отмечены галочками на вкладке Net Manager цепь земли и три шины питания.

Если бы я ввел в программу для расчета и другие цепи питания (2,5 В, 3,3 В и т.д.), а мне необходимо было бы промоделировать только одну, то нужно чтобы в таблицах Voltage Drop Analysis Setup были отмечены только те источники напряжения, потребители и межсоединения, для которых отмечены галочками все необходимые шины питания и цепи земли на вкладке Net Manager! Если будет несовпадение, то не будет хватать данных для расчета, и программа выдаст ошибку. Поэтому после ввода всех рассчитываемых цепей проще отметить галочками все и промоделировать все за один раз, а потом уже на вкладке Net Manager выключить отображение ненужных.

12. Проверяем схему на наличие ошибок, нажав на Check Errors/Warnings в меню Single—Board/Package IR Drop Analysis, а затем сохраняем файлы, нажав Save Files, после чего запускаем моделирование проекта, нажав на Start Simulation.

6. Анализ результатов моделирования, выработка рекомендаций по коррекции разводки, корректировка разводки печатной платы.

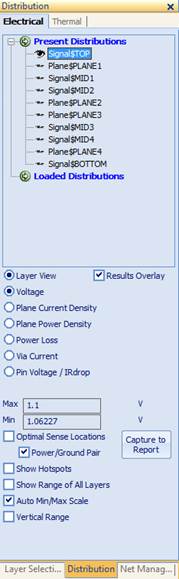

В группе пунктов меню Results and Report, нажав на Single—Board/Package IR Drop Analysis, можем посмотреть результаты моделирования либо в виде таблицы, выбрав отображение в виде таблицы (View E—Results Tables), либо в двумерном виде (View 2D E—Distributions), либо в трехмерном виде (View 3D E—Distributions).

После симуляции слои для отображения выбираются на вкладке Layer Selection справа. Внизу можно выбрать, какие элементы слоя отображать: дорожки (Trace), отверстия (Via), контактные площадки (Pad), шины (Node) и т.д. (рис. 6.1).

Рис. 6.1. Вкладка Layer Selection

На вкладке Distribution (рис. 6.2) тоже можно переключаться между слоями, кроме этого, здесь настраивается вид отображаемого расчета:

· напряжение (Voltage);

· плотность тока (Plane Current Density);

· плотность мощности (Plane Power Density);

· потери мощности (Power Loss);

· ток через отверстия (Via Current);

· напряжения на пинах/разброс напряжений (Pin Voltage/IRdrop).

При этом чуть ниже для каждого вида анализа появляются дополнительные опции настройки (например, можно отобразить векторное поле для анализа плотности тока).

Рис. 6.2. Вкладка Distribution

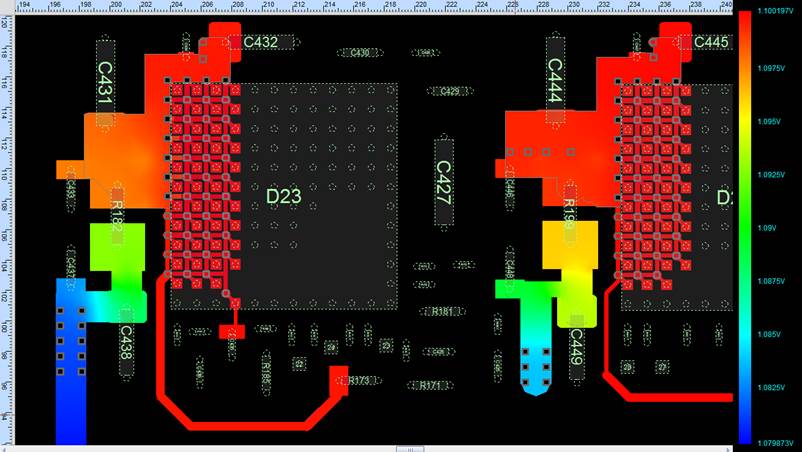

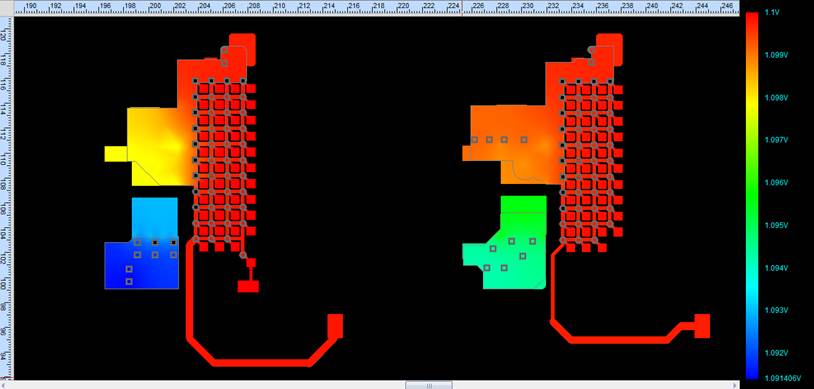

Нас особенно интересует напряжение на потребителе. Внизу, в таблице результатов расчета, на вкладке Sink Voltage указано среднее напряжение на контактах потребителя (Actual Voltage). Чтобы посмотреть разброс напряжений и их величины на контактах потребителя, необходимо выбрать на вкладке Distribution вид отображаемого анализа Pin Voltage/IRdrop и по шкале или в полях внизу посмотреть распределение напряжений на контактах потребителя.

Мы видим, что расчетное напряжение примерно 1,0424 В, или меньше на 0,0576В от требуемого 1,1 В. Получается, что падение напряжения на дорожках составляет 5,24%. Погрешность установки выходного напряжения для источников питания данного типа составляет 1,5%, следовательно, возможное наибольшее падение напряжения будет 6,73%, что много, так как для данного потребителя точность установки напряжения должна составлять 5%. Следовательно, необходимо редактировать печать.

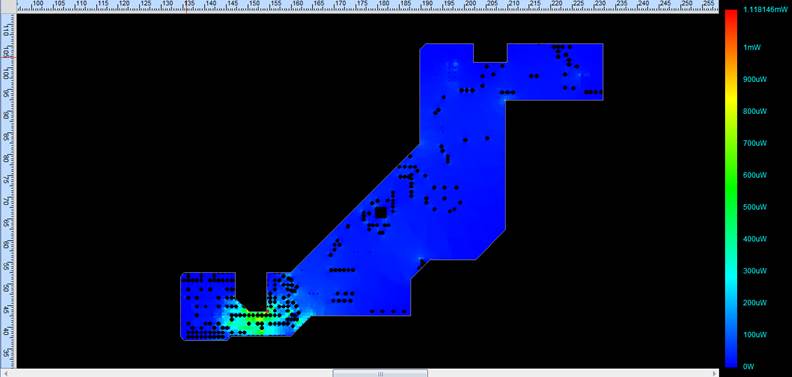

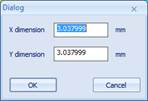

Посмотрим, что можно улучшить. Имеем следующую картину в слое Plane3 (рис. 6.3):

Рис. 6.3. Слой Plane3, цепь PLIS_VCCL_1_1V, вид отображения напряжения (Voltage)

То место, в котором происходит более быстрая смена цветов и есть самое плохое, на которое надо обратить внимание. Удобно, что шкала автоматически перестраивается в зависимости от участка цепи, изменяя максимальное, минимальное значение и шаг! С помощью этой функции есть возможность быстро узнать величину падения напряжения на каком-то участке цепи, если есть возможность изолировано отобразить его на экране. Кроме этого, величину падения напряжения на участке можно узнать либо приблизительно по цветовой шкале, либо навести курсор на нужное место цепи и посмотреть значение, вычислив падение между двумя точками. Видно, что на узком участке внизу теряется порядка 5,7мВ или примерно 0,5%.

Узкие места (в плане расчетного падения напряжения на единицу длины) хорошо видно, если установлен режим просмотра потерь мощности (Power Loss) на вкладке Distribution (рис. 6.4):

Рис. 6.4. Слой Plane3, цепь PLIS_VCCL_1_1V, вид отображения потерь мощности (Power Loss)

При этом видно, что участок, где больше всего теряется мощность, подсвечен более ярким цветом. Посмотрим, что можно ещё исправить в других слоях. Так, например, в верхнем слое рядом с проходными резисторами узкие дорожки к переходным отверстиям из-за тепловых зазоров элементов (рис. 6.5). Можно убрать тепловые зазоры, расширить дорожки и расположить ближе переходные отверстия. Таким образом, уменьшится и падение напряжения, и плотность тока.

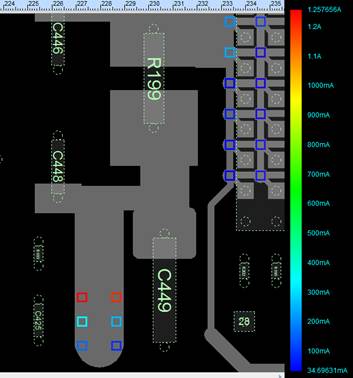

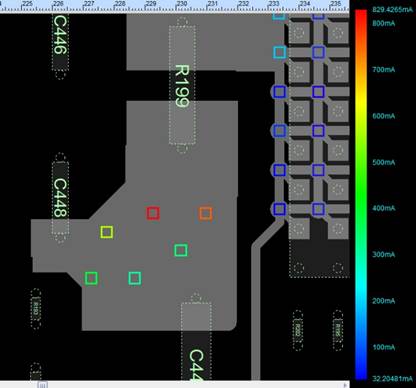

Кроме этого, сами переходные отверстия расположены далеко не оптимально, так как большая часть тока утекает в крайние отверстия, а в остальных величина протекающего тока гораздо меньше (рис. 6.6).

Рис. 6.5. Слой Top, цепи VCC1_1_1, VCC2_1_1, PLIS_VCCL_1_1V, вид отображения напряжения (Voltage)

Рис. 6.6. Слой Top, цепи VCC2_1_1 и PLIS_VCCL_1_1V, вид отображения тока через переходные отверстия (Via Current)

В программе PowerDC можно откорректировать разводку печатной платы. Для этого используются инструменты, расположенные на панелях инструментов Shape, Select, Object.

С помощью инструментов панели Shape (рис. 6.7) можно добавлять «вычитающие» и «прибавляющие» элементы печати (прямоугольники, круги, полигоны) и проводить операции с вершинами полигонов. Вычитающие полигоны действуют только на другие полигоны, а не на шины!

![]()

Рис. 6.7. Панель инструментов Shape

С помощью инструментов панели Select (рис. 6.8) можно выбрать элементы печати (полигоны, шины, отверстия и т.д.) которые будут отображаться на плате.

![]()

Рис. 6.8. Панель инструментов Select

Панель инструментов Object (рис. 6.9) позволяет добавлять и редактировать шины, переходные отверстия и т.д.

![]()

Рис. 6.9. Панель инструментов Object

Если навести курсор на иконку инструмента, то появится его название. Для редактирования печати слоя переключимся в режим отображения печати, нажав на пункт Switch to Normal Layer View раздела Results and Report меню Single—Board/Package IR Drop Analysis. Затем нажмем на иконку Show Vertices панели инструментов Shape, чтобы отобразить вершины полигонов для облегчения редактирования формы полигона. После этого воспользуемся инструментом Delete Vertex этой же панели инструментов, чтобы удалить ненужные вершины у этого и соседнего полигона. Интересно посмотреть, насколько лучше станет ситуация с этой цепью питания, поэтому после редактирования нажимаем на кнопку Start Simulation и ждем результатов симуляции (рис.6.10).

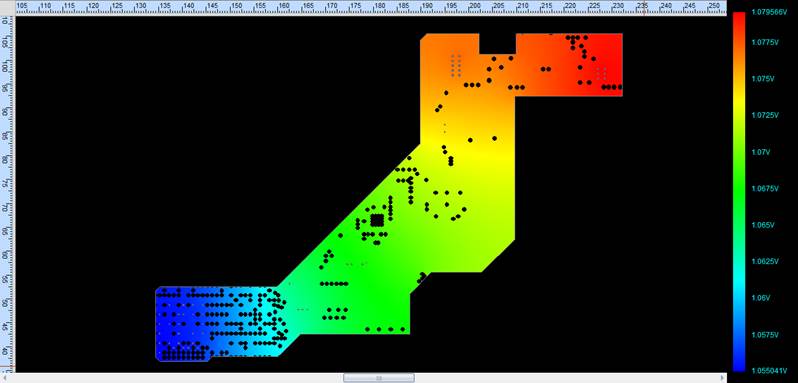

Рис. 6.10. Слой Plane3, цепь PLIS_VCCL_1_1V, вид отображения напряжения (Voltage)

После симуляции видим, что на этом участке цепи минимальное напряжение увеличилось примерно с 1,048 мВ до 1,055 мВ или на 0,6%, а минимальное напряжение на потребителе теперь равно 1,049 мВ. Таким образом, падение напряжения относительно источника 1,1В стало 4,64%. Это всё ещё много, поэтому необходимо изменить печать в верхнем слое и убрать тепловые зазоры, а также изменить местоположение переходных отверстий.

После редактирования снова осуществляем моделирование и смотрим результаты. Распределение токов по переходным отверстиям стало более равномерным (рис. 6.11 и таблица 6.1), а падение напряжения на этом участке стало меньше примерно на 0,0116 В, что составляет примерно 1% от 1,1В (сравнение рис. 6.5 и рис. 6.12).

Рис. 6.11. Слой Top, цепи VCC2_1_1 и PLIS_VCCL_1_1V, вид отображения тока через переходные отверстия (Via Current)

Таблица 6.1. Сравнение двух вариантов разводки печатной платы по плотности тока и абсолютной величине тока через переходные отверстия

|

№ пер. отв. |

Вариант 1 (до оптимизации), плотность тока (А/мм2); ток (мА) |

Вариант 2 (после оптимизации), плотность тока (А/мм2); ток (мА) |

|

1 |

17,8; 1258 |

11,7; 829 |

|

2 |

17,1; 1210 |

10,7; 757 |

|

3 |

4,6; 326 |

8,0; 568 |

|

4 |

3,6; 253 |

4,8; 343 |

|

5 |

2,3; 161 |

5,5; 392 |

|

6 |

1,3; 93 |

4,4; 308 |

Рис. 6.12. Слой Top, цепи VCC1_1_1, VCC2_1_1, PLIS_VCCL_1_1V, вид отображения напряжения (Voltage)

Минимальное напряжение на контактах потребителя стало 1,062 В, т.е. выше на 0,013 В или на 1,19%. Итого падение напряжения составляет 3,45%, а с учетом погрешности установки источника питания (1,5%) максимально возможное отклонение будет равно 4,95%, что уже соответствует требованиям к погрешности установки напряжения для потребителя. Кроме этого, в новой версии печатной платы входы обратной связи источника питания были подключены к более близко лежащей точке к потребителю, чем раньше, что увеличивает запас более чем на 0,05%. В результате эту цепь питания было решено оставить в таком виде и перейти к анализу других.

7. Замечания по работе с программой.

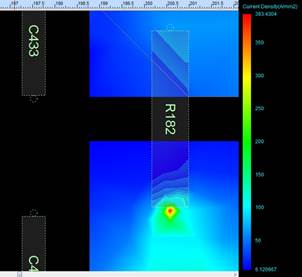

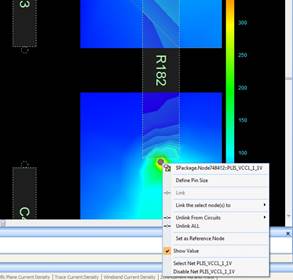

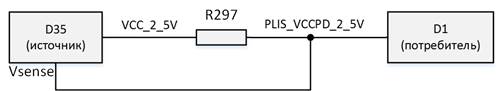

1. Первоначально при выводе результатов анализа плотности тока у меня был некорректный расчет на контактных площадках элементов – получалось, что как будто это элементы не поверхностного, а навесного монтажа, и ток течет через точки, в которых получается очень большая плотность тока (на рис. 7.1 порядка 390 А/мм2). Из проекта Altium Designer в PowerDC размеры пинов импортируются как надо (согласно размерам контактных площадок), но расчет у меня производился некорректно. Проблема была решена при переопределении размеров пинов. Для этого необходимо включить на вкладке Distribution вид отображения Plane Current Density, отображение цепей (Node) и элементов (Circuit), а затем щелкнуть правой кнопкой на той цепи, которая присоединяется к элементу (обозначена серой точкой в кружочке на конце элемента) и выбрать определение размера Define Pin Size (рис. 7.2). В появившемся окне, не изменяя значения, нажать OK (рис. 7.3) и произвести повторную симуляцию. Как видно на рисунке 7.4, расчет теперь производится корректно.

Рис. 7.1. Пример результатов неверного расчета плотности тока (Plane Current Density)

Рис. 7.2. Вызов меню определение размера пина (Define Pin Size)

Рис. 7.3. Окно определения размеров пина

Рис. 7.4. Пример результатов корректного расчета плотности тока (Plane Current Density)

2. После того, как я ввел все цепи питания печатной платы аналогично приведенным выше пунктам, то у меня производился неверный расчет цепей, которые используются для коррекции выходного напряжения источников питания. Для примера рассмотрим цепь питания, показанную на рисунке 7.5. Так как микросхема D35 была введена как источник напряжения (VRMs), то и цепь обратной связи воспринималась как выходная, а не как входная.

Рис. 7.5. Схематическое изображение цепи питания со входом обратной связи источника

Для того, чтобы расчет схемы проводился корректно, необходимо было сделать следующее:

· Добавить микросхему как источник по цепи питания согласно пункту 5.5.

· Добавить эту же микросхему как потребитель по необходимой цепи, согласно пункту 5.6.

· Выбрать на вкладке Distribution вид отображения Plane Current Density, отображение цепей (Node) и элементов (Circuit) и щелкнуть правой кнопкой по выводу (серая точка Node на контактной площадке микросхемы), который необходимо настроить. В появившемся меню выбираем Unlink From Circuits→Unlink VRM или Unlink SINK (в зависимости от назначения вывода разрываем ненужную связь, либо от источника (VRM), если вывод – входной, либо от потребителя (SINK), если это вывод источника напряжения) и далее выбираем либо нужную связь, либо разрываем все связи, если их несколько и надо разорвать все.

Так как микросхема D35 в моей схеме является источником питания, а контакт Vsense должен был быть как потребитель с маленьким входным током, то мне необходимо было выбрать Unlink From Circuits→Unlink VRM и разорвать связь с источником для этого контакта (рис. 7.6).

Рис. 7.6. Меню выбора разрыва связи для контакта микросхемы, режим отображения плотности тока (Plane Current Density)

8. Заключение

После того, как был проведен анализ цепей питания в программе PowerDC, был выработан список рекомендаций для завода по редакции печатной платы. Какие-то пункты они смогли реализовать, а какие-то нет, поэтому пришлось делать несколько итераций редактирования и анализа с рассмотрением нескольких вариантов печати. Сложность разводки цепей питания на плате заключается в наличии большого количества дифференциальных пар и линий, для которых необходимо выдержать значение импеданса. Поэтому параллельно с анализом цепей питания необходимо было выполнять анализ дифференциальных пар и значения импеданса линий. Эта возможность тоже существует в пакете программ Allegro Sigrity Cadence, но это уже тема для другой статьи. =)

(2 оценок, среднее: 5,00 из 5)

(2 оценок, среднее: 5,00 из 5)

4 thoughts on “Анализ цепей питания печатной платы в программе PowerDC пакета Allegro Sigrity Cadence”